Generate Compilers from Hardware Models!

Gus Henry Smith, Ben Kushigian, Vishal Canumalla, Andrew Cheung, René Just, Zachary Tatlock

Workshop on Programming Languages and Computer Architecture (PLARCH) 2023

Abstract

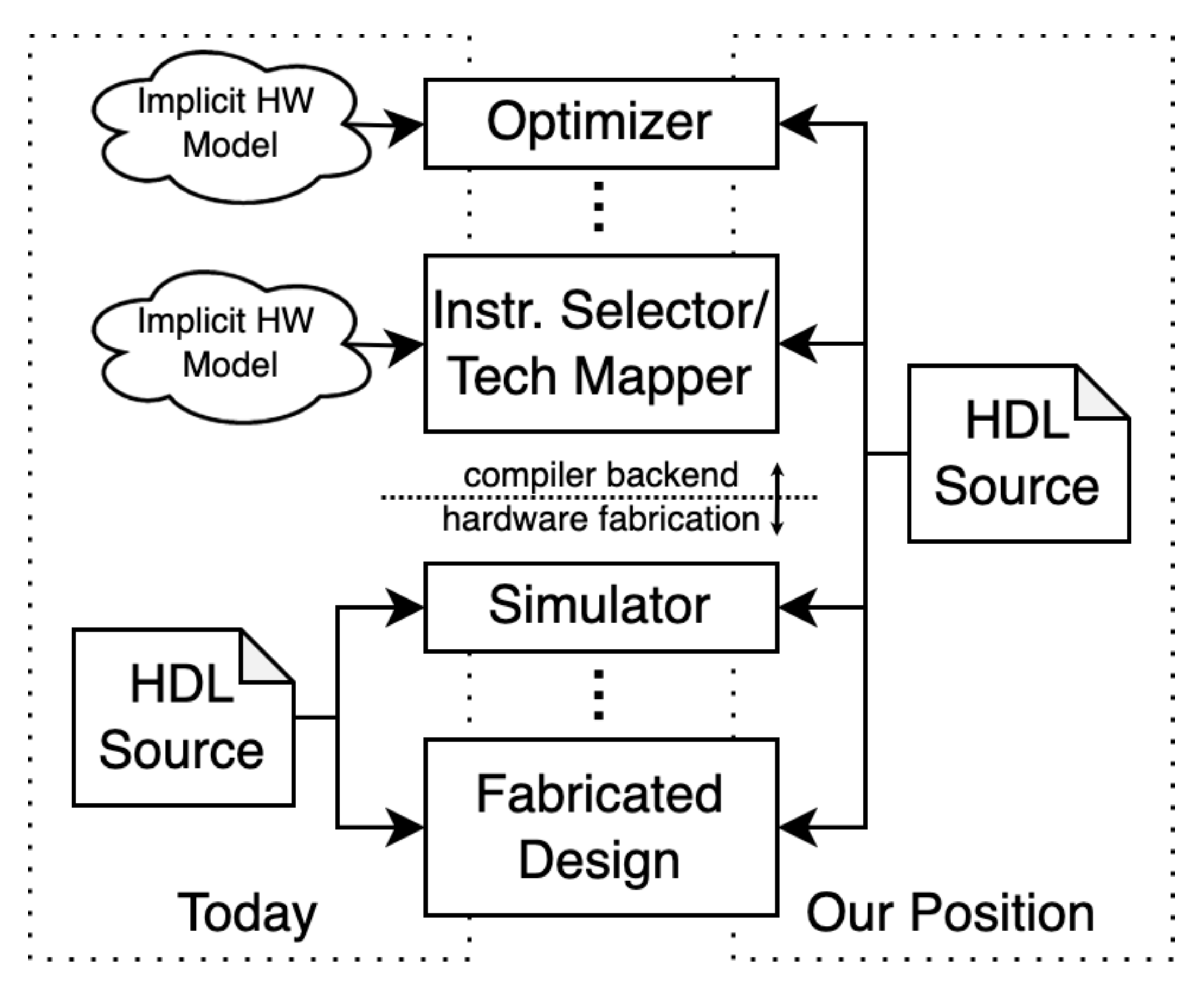

Compiler backends should be automatically generated from hardware design language (HDL) models of the hardware they target. Generating compiler components directly from HDL can provide stronger correctness guarantees, ease development effort, and encourage hardware exploration. Past work has already championed this idea; here we argue that advances in program synthesis make the approach more feasible. We present a concrete example by demonstrating how FPGA technology mappers can be automatically generated from SystemVerilog models of an FPGA’s primitives using program synthesis.

Talk

PLARCH 2023 talk by Gus Smith.

BibTeX

@inproceedings{2023-plarch-lakeroad,

title = {Generate Compilers from Hardware Models!},

author = {Gus Henry Smith and Ben Kushigian and Vishal Canumalla and Andrew Cheung and René Just and Zachary Tatlock},

series = {PLARCH 2023},

booktitle = {Workshop on Programming Languages and Computer Architecture (PLARCH) 2023},

publisher = {Association for Computing Machinery},

}